#

## High Mobility Flexible Graphene Field-Effect Transistors with Self-Healing Gate Dielectrics

Chun-Chieh Lu,<sup>†</sup> Yung-Chang Lin,<sup>†</sup> Chao-Hui Yeh,<sup>†</sup> Ju-Chun Huang,<sup>‡</sup> and Po-Wen Chiu<sup>†,\*</sup>

<sup>†</sup>Department of Electrical Engineering and <sup>‡</sup>Center for Nanotechnology, Materials Science and Microsystems, National Tsing Hua University, Hsinchu 30013, Taiwan

ne of the obstacles to the development of flexible electronics has been creating transistors with high carrier mobility, yet stable enough to function in a variety of environments. Organic semiconductor materials offer a flexible platform for use as active components in field-effect transistors (FETs), opening up a variety of promising applications in lightweight, low-cost, and low-power switching components, such as active-matrix elements for plastic displays,<sup>1–4</sup> sensor arrays,<sup>5,6</sup> radio frequency identification tags,<sup>7</sup> and flexible logic circuits.<sup>8,9</sup> However, the carrier mobility of organic materials is low, typically ranging from  $10^{-3}$  to  $1 \text{ cm}^2/\text{V} \cdot \text{s}$  due to the weak van der Waals interaction between  $\pi$ -conjugated molecules leading to hopping conduction. Graphene is a singleatomic layer macromolecule with promise as a high-speed platform for flexible and transparent FETs built on soft substrates. Chen et al. reported fabricating flexible graphene FETs via the transfer printing method, transferring mechanically exfoliated graphene flakes and predefined electrodes to a plastic substrate for device assembly.<sup>10</sup> For practical applications, large-scale graphene films grown by chemical vapor deposition (CVD) are desirable, as is fabrication compatibility with silicon technology. Currently, flexible FETs using CVD graphene as a channel material have only exhibited an electron mobility of  $\sim$ 90 cm<sup>2</sup>/V·s.<sup>11</sup> This is presumably due to the long access lengths (i.e., the ungated channel region between the drain/source contacts and gate), downgrading device performance through the parasitic resistance  $R_A$ .<sup>12</sup> Farmer *et al.* showed that self-aligned top gates fabricated using the hydrophobic characteristics of the surface of exfoliated graphene can minimize the access length,12 yielding a greatly increased carrier mobility and cutoff frequency in the resulting FETs. However,

A high-mobility low-voltage graphene field-effect transistor (FET) array was fabricated on a flexible plastic substrate using high-capacitance natural aluminum oxide as a gate dielectric in a self-aligned device configuration. The high capacitance of the native aluminum oxide and the self-alignment, which minimizes access resistance, yield a high current on/off ratio and an operation voltage below 3 V, along with high electron and hole mobility of 230 and  $300 \text{ cm}^2/\text{V} \cdot \text{s}$ , respectively. Moreover, the native aluminum oxide is resistant to mechanical bending and exhibits self-healing upon electrical breakdown. These results indicate that self-aligned graphene FETs can provide remarkably improved device performance and stability for a range of applications in flexible electronics.

**KEYWORDS:** graphene · field-effect transistor · self-alignment · chemical vapor deposition · flexible electronics

the hydrophobic surface of large-area CVD graphene is usually obscured by a thin layer of polymer residue due to the transfer process.<sup>13,14</sup> The inhomogeneous coverage of the polymer residue frequently results in pinholes in the stack of high- $\kappa$  dielectrics (*e.g.*, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and ZrO<sub>2</sub>) grown by atomic layer deposition (ALD). The high temperatures used in the ALD process may also rule out the use of some plastic substrates.<sup>15–17</sup>

This paper describes the fabrication of self-aligned CVD graphene FETs on a plastic substrate, using naturally formed aluminum oxide as a gate dielectric and spacer for selfalignment. The fabrication process is not \* Address correspondence to pwchiu@ee.nthu.edu.tw.

Received for review March 19, 2012 and accepted April 13, 2012.

Published online April 13, 2012 10.1021/nn301199j

© 2012 American Chemical Society

VOL.6 • NO.5 • 4469-4474 • 2012

12 ASNANC www.acsnano.org

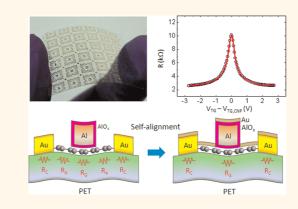

Figure 1. (a) Schematic diagram of the steps used to fabricate self-aligned graphene FETs on a Si substrate. The lower panel shows the critical resistive components before and after the self-alignment. (b) SEM image of self-aligned graphene FETs with different gate lengths (300 nm, 700 nm, and 2  $\mu$ m). The channel width of all devices is 10  $\mu$ m. The optical photograph in the inset shows the overall device layout. The self-aligned source/drain electrodes are separated by AlO<sub>x</sub> spacers in each device. (c) TEM image of the detailed device layout in the vicinity of AlO<sub>x</sub> spacer. (d) TEM image of AlO<sub>x</sub> grown deeply at the interface between graphene and Al.

restricted by graphene surface characteristics, and hence neither predefined buffer layers nor chemical functionalization on the graphene surface are required prior to the deposition of gate dielectrics. The access resistance in the graphene channels is minimized, resulting in high electron mobility that is potentially comparable with exfoliated graphene on SiO<sub>2</sub>/Si, and does not degrade upon bending to a radius R > 8 mm. The natural AlO<sub>x</sub> possesses high gate capacitance and exhibits the unique property of self-healing upon electrical breakdown. The damaged alumina dielectric layer can be healed using mild electrical annealing or aging in air, both repairing the dielectric without noticeable increase in leakage current or downgrading of electron mobility.

### **RESULTS AND DISCUSSION**

Before fabricating graphene FETs on plastic substrate, we first produced graphene FETs on Si substrate with dual gates to better characterize the alumina gate dielectric. The cross-sectional device layout is schematically shown in the left panel of Figure 1a. In the conventional top-gated graphene FETs, a long access length usually exists between the gate and drain/source electrodes. The ungated graphene channel stays in a highly resistive state because the Fermi level is located in the vicinity of the conical points of band structure, which possess low density of electronic states. It results in a total resistance which consists of contact resistance  $R_{C_{i}}$  access resistance  $R_{A_{i}}$  and gated resistance  $R_{G_{i}}$ as schematically shown in the lower left panel of Figure 1a. The access resistance usually turns out to be a dominant component in the total resistance as downscaling the graphene FET and negatively impacts device performance. It is therefore desirable to shorten the access length as much as possible. For a graphene FET with dual gates, a facile way to modulate the carrier density in the access graphene channel is by applying a back-gate voltage. However, it becomes inaccessible for graphene FETs built on a nonconductive plastic substrate. To minimize  $R_A$  in a single-gating configuration, fabrication of self-aligned drain/source contacts provides a technically feasible solution and can be applied to all sources of planar graphene and plastic substrates.

Graphene used for device fabrication was grown by low-pressure CVD technique on Cu foil,<sup>18</sup> followed by a wet transfer process using poly(methyl methacrylate) (PMMA) as a scaffold. Detailed graphene characterizations can be found in Supporting Information. A graphene strip was then defined by e-beam lithography in combination with oxygen plasma etching. Source/ drain electrodes (0.5 nm Cr/60 nm Au) and an Al top gate (70 nm) were made by two-step e-beam lithography and thermal evaporation. No additional dielectric layer between the Al and graphene was introduced. Following Al evaporation, the devices were exposed to air for at least 6 h to form a thin  $AIO_x$ dielectric layer around the Al wire.<sup>19,20</sup> Another layer of Cr (0.5 nm)/Au (10 nm) was deposited on a patterned region, completely covering the graphene strip. This deposition was automatically aligned by the Al/AlO<sub>x</sub> gate edges and separated into two isolated regions, forming the source and drain electrodes. This process reduced the access length to  $\sim$ 20 nm, mainly the length underneath the spacer.

Figure 1b shows a scanning electron microscopy (SEM) image of self-aligned graphene FETs on a Si substrate with different gate lengths, while the inset shows an optical photograph of the overall device layout. For the self-alignment, the spacers that separate source/drain from gate electrode are constituted of natural AlO<sub>x</sub>, which is electrically robust and exhibits the unique feature of self-healing upon breaking down. Figure 1c shows the cross-sectional transmission electron microscopy (TEM) image of a spacer. The source/drain electrodes are well separated by the Al/AlO<sub>x</sub> gate electrode and are precisely positioned next to the spacers. The average access length measured by TEM is about 20 nm. Figure 1d shows a high-resolution TEM image of the AlO<sub>x</sub>/graphene interface. The AlO<sub>x</sub>

layer is found to form around the Al wire and penetrates deep into the interface between the Al and graphene following exposure to air over 6 h at room temperature. The oxidation can be expedited using current-induced annealing. The thickness of the oxide layer ranges from 5 nm (embedded at the graphene/Al interface) to 12 nm (exposed to the air) (see Supporting Information for more details). The natural AlO<sub>x</sub> on CVD graphene provides a negligible leakage current within

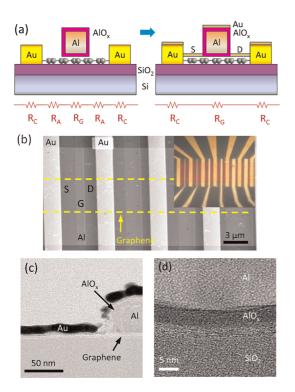

Figure 2. Device properties of self-aligned graphene FETs on a silicon substrate. (a) Transfer characteristics of a device before (red curve) and after (blue curve) self-alignment. (b) Corresponding transconductance of the curves shown in (a). (c) Transfer characteristics of a self-aligned device. The bottom-gate is swept between -10 and -50 V in 10 V steps. (d) Dirac voltage varies linearly with the top- and back-gate voltages.

the gate sweep range of  $\pm 2.5$  V, while typical leakage current is <100 pA. Compared with organic FETs using natural AlO<sub>x</sub> as a gate dielectric, the leakage current in our CVD graphene FETs is noticeably suppressed. This is attributed to the presence of residual PMMA (1–2 nm) on the graphene,<sup>13,14</sup> which resembles the self-assembled monolayer on AlO<sub>x</sub> as a hybrid dielectric.<sup>5,21,22</sup>

Figure 2a,b shows the impact of self-alignment on the same CVD graphene transistor with a channel width  $W = 5 \,\mu\text{m}$  and channel length  $L = 2 \,\mu\text{m}$ . A total access length of 4  $\mu$ m is eliminated following selfalignment. The transfer characteristics and corresponding transconductances of the device show the benefits of self-alignment. Following self-alignment, the maximum  $I_{ON}/I_{OFF}$  ratio is increased from 1.2 to 3.2, and the maximum transconductance,  $g_m = |dI_{DS}/dV_G|$ , also rises by an order of magnitude at  $V_{DS} = 1$  mV for both electron and hole. To better understand device performance, the top-gate dielectric capacitance  $C_{TG}$ is obtained by measuring the drain current at varying top-gate  $V_{TG}$  or back-gate  $V_{BG}$  sweeps (Figure 2c). The charge neutrality point at each  $V_{TG}$  sweep ( $V_{TG,CNP}$ ) exhibits a linear shift as a function of the  $V_{BG}$ (Figure 2d), from which we can determine  $C_{TG}$  using the simple capacitance equation, Q = CV. The top-gate capacitance is written as  $C_{TG} = -C_{BG}(\Delta V_{BG}/\Delta V_{TG})$ , yielding  $C_{TG}/C_{BG} \approx$  86 from the slope of Figure 2d. For 300 nm thick SiO<sub>2</sub>,  $C_{BG}$  is 11.6 nF/cm<sup>2</sup>. The top-gate dielectric capacitance is found to be  $C_{TG} = 998 \text{ nF/cm}^2$ . Using the capacitance model for parallel plates, the permittivity of the AlO<sub>x</sub> layer is determined to be  $\varepsilon_{TG}$  =  $C_{\text{TG}}d_{\text{TG}}/\varepsilon_0$  =5.65 for  $d_{\text{TG}}$  = 5 nm, a value typically found in a natural  $AIO_x$  thin film.<sup>23</sup>

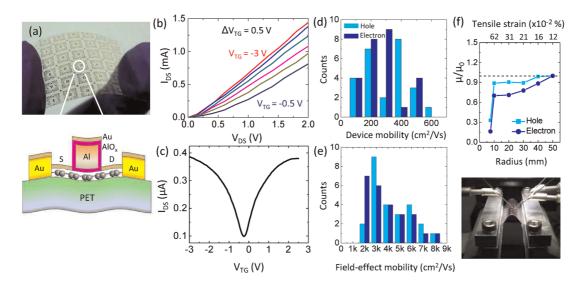

Figure 3a shows the flexibility of self-aligned graphene FETs fabricated on poly(ethylene terephthalate) (PET),

Figure 3. Electrical and mechanical properties of self-aligned graphene FETs fabricated on a flexible substrate. (a) Optical photograph of an array of devices on a PET substrate, with a schematic drawing showing the device layout. (b) Output characteristics of graphene FETs on PET. The gate voltage was applied between -0.5 and -3 V in -0.5 V increments. (c) Transfer characteristics of graphene FETs on PET. (d) Histogram of device mobility. (e) Histogram of intrinsic field-effect mobility. (f) Normalized mobility as a function of the bending radius and tensile strain.

4471

using the same fabrication process as that used for devices made on rigid substrates (details are provided in the Supporting Information). Figure 3b,c shows the typical output and transfer characteristics of the resulting devices. No apparent degradation of device characteristics is found as compared with those fabricated on SiO<sub>2</sub>. This is attributed to the fact that graphene devices fabricated on SiO<sub>2</sub> suffer from additional scattering associated with low-energy surface phonon. Substantial trap density in SiO<sub>2</sub> also results in appreciable decrease of device mobility. However, for the graphene lying on the PET substrate, the nanoscale surface roughness (see Supporting Information) makes the transferred graphene film semisuspended, mitigating the surface phonon and trapped charge scatterings. Although the carrier mobility may be deteriorated by the local strains, the measured intrinsic carrier mobility on PET is found to be similar to that on SiO<sub>2</sub>. The charge neutrality point in the transfer characteristics deviates from  $V_{TG} = 0$  due to the weak electron doping of the gate.<sup>24,25</sup> The  $I_{ON}/I_{OFF}$  ratio falls in the range of 3–6, and the  $g_{\rm m}$  is 300–500 nS. Using  $\mu_{\rm DEV}$  =  $q_{\rm m}L/V_{\rm DS}WC_{\rm TG}$ , these transconductances can be translated into device mobilities, as shown in Figure 3d. The respective mean device mobilities for electron and hole are 230 and 300 cm<sup>2</sup>/V·s. Compared with other reported flexible FETs, such as amorphous silicon, polycrystalline silicon, organic materials, and carbon nanotubes, our self-aligned flexible graphene FETs exhibit improved mobility (see Supporting Information). To gain further insight into the intrinsic carrier mobility, we adopt the model described in ref 26 to fit the transfer characteristics in the form of a  $R_{\rm DS} - V_{\rm TG}$  plot. The device's total resistance  $R_{\rm T}$  can be expressed using the following equation which contains the contact resistance  $R_{Cr}$  access resistance  $R_{Ar}$  and the intrinsic graphene channel resistance covered by the gate electrode:

$$R_{\rm T} = 2R_{\rm C} + 2R_{\rm A} + \frac{L_{\rm G}}{We\mu_{\rm FE}\sqrt{n_0^2 + n_{\rm TG}^2}}$$

where  $L_{\rm G}$  and  $n_0$ , respectively, are the gate length and residual carrier density at the charge neutrality voltage. The carrier density induced by the top gate is calculated with  $n_{\rm TG} = C_{\rm TG}(V_{\rm TG} - V_{\rm TG,CNP})/e$ . Figure 3e shows the histogram of field-effect mobility refitted using the above equation. Each fitting gives the residual carrier density  $n_0$ ,  $2(R_{\rm C} + R_{\rm A})$ , and field-effect mobility  $\mu_{\rm FE}$ . Due to the negligible  $R_{\rm A}$  in the self-aligned devices, their series resistance is dominated by the metal contacts. The mean contact resistance  $R_{\rm C}$  in our devices is  $\sim 2 \,\rm k\Omega$ . The  $\mu_{\rm FE}$  increases by an order of magnitude after subtracting the contact resistance and ranges from 2000 to 8000 cm<sup>2</sup>/V·s. The wide mobility distribution may result partly from the variation of graphene quality such as the formation of bi- and trilayer graphene in part of the large-area graphene film (Figure S2 in Supporting Information) and partly from the inhomogeneous PMMA residue that causes substantial variation of the hybrid gate capacitance. The high contact resistance is responsible to the low device mobility shown in Figure 3d. Lowering the contact resistance is, therefore, as important as minimizing the access resistance so as to obtain high device mobility in graphene FETs. It was also found that bending the substrate to a radius of R > 8 mm does not cause apparent changes in the  $R_{DS}-V_{TG}$  curves or the mobility (Figure 3f), indicating that bending causes no degradation in the graphene channel or contacts.

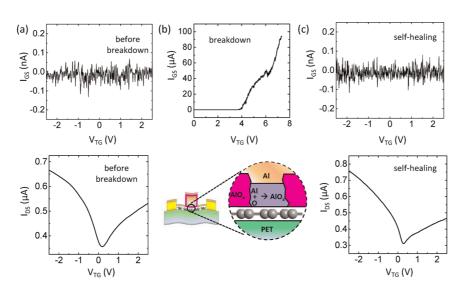

The natural  $AIO_x$  not only acts as the spacer for selfalignment but also self-heals upon electrical breakdown.<sup>27</sup> To explore the self-healing of alumina on graphene, dielectric breakdown was intentionally triggered by progressively increasing the gate-source voltage to exceed the breakdown field. The dielectric strength of a material is essentially dependent on the configuration of the material or the electrodes by which the field is applied. For natural alumina formed on transferred CVD graphene, the breakdown field is  $\sim$ 5 MV/cm, provided that the breakdown occurs at the thinnest part. Dielectric breakdown results in an abrupt and considerable increase of current flowing through the oxide (Figure 4a,b), and the V-shaped ambipolar conduction vanishes in the gate sweeps due to the loss of potential modulation by the gate. At the high field, the  $I-V_{GS}$  curves become irreversible, indicating physical damage such as pinholes or nanocracks in the oxide.

The damaged oxide can be restored automatically through several hours of air exposure or alternatively through electrical annealing to expedite the healing rate (see Supporting Information). Fresh native oxide can regenerate in the vicinity of the damaged areas, though the gate oxide is sandwiched by graphene and aluminum, effectively reducing the leakage current to a level comparable to that of the pristine state. The lower panels in Figures 4a and 4c compare the transfer characteristics of a device before and after self-healing in air, showing that device properties including current on/off ratio, transconductance, and charge mobility are nearly fully restored following the repair. For selfhealing by aging in air, temperature and humidity are the major parameters that affect the reaction rate. Generally, it takes  $\sim$ 6 h to regrow the native oxide to sufficient thickness, indicating that diffusion of H<sub>2</sub>O or O<sub>2</sub> into the graphene/Al interface is the rate-limiting step. It should be noted that the involvement of H in the oxide creates electronic defects<sup>28</sup> that tail a few electronvolts from the band edges to deep within the oxide gap.<sup>29</sup> At the high field, electronic conduction (gate leakage) can occur via carrier tunneling through the triangular barrier into a defect level in the oxide.<sup>30</sup> It is, therefore, possible to assess the quality of the

ARTICLE

agnanc www.acsnano.org

Figure 4.  $I_{GS}-V_{GS}$  and  $I_{DS}-V_{GS}$  curves of a graphene FET on PET. (a) Before the AIO<sub>x</sub> dielectric breakdown. (b)  $I_{GS}-V_{GS}$  curve at the breakdown. The lower panel is a schematic drawing showing the regrowth of native AIO<sub>x</sub> at the breakdown site. (c) Following self-healing of the AIO<sub>x</sub> layer by aging in air for 6 h.

natural aluminum oxides from the  $I_{GS} - V_{TG}$  curve shown in Figure 4b.

#### CONCLUSIONS

We present a type of flexible graphene FET with a self-aligned gate. The naturally formed aluminum oxide acts as a high-quality gate dielectric and spacer for the formation of self-aligned drain/source contacts. This self-aligned process can be applied to different graphene sources, irrespective of graphene surface

#### **METHODS**

**Graphene Growth.** Graphene sheets used in the current study were grown by low-pressure CVD of methane (99.99%) on polycrystalline Cu foils. Prior to growth, the Cu foils were cleaned by acetone and isopropyl alcohol (IPA) with sonication, followed by etching in acetic acid for 30 min to remove surface oxides. Then, the Cu foil was mounted in the CVD chamber with a steady flow of 10 sccm hydrogen. The furnace was ramped up to 1000 °C over 40 min. In the CVD process, methane (20 sccm) mixed with hydrogen (10 sccm) was fed into the reaction chamber for 10 min at the pressure of about 2.1 Torr. After the growth, the Cu foil was moved to the cooling zone without changing the hydrogen flow. The characterization results of our CVD graphene are provided in Supporting Information.

**Device Fabrication.** Graphene FETs were made with e-beam lithography and standard lift-off process. PMMA in a two-layer structure (996 and 120 K) was spin-coated on the graphene film, followed by baking at 130 °C for 30 min. E-beam lithography was carried out using a scanning electron microscope (JSM-840A) equipped with an e-beam writer (Elphy Quantum, Raith). The exposed PMMA was then developed with methyl isobutyl ketone (MIBK) and IPA in a ratio of 1:3. Metal contacts were evaporated after the development. Keithley 2400 and 2000 were, respectively, used as a current/voltage source and multimeter for current–voltage measurements. All of the devices were measured in ambient conditions in a two-probe configuration.

Conflict of Interest: The authors declare no competing financial interest.

conditions, thus allowing for device fabrication using large-area CVD graphene, even with polymer residues on the surface. The access length is greatly reduced to 20 nm, resulting in relatively high device mobilities of 150-230 and 260-300 cm<sup>2</sup>/V·s, respectively, for electron and hole. Moreover, the aluminum gate provides low-voltage device operation, which should facilitate future implementation of logic gates. This method represents a significant step in the application of graphene to flexible electronics.

Acknowledgment. The authors appreciate the support from the NTHU booster project and Taiwan National Science Council under Contract No. NSC 100-2112-M-007-014-MY3.

Supporting Information Available: Additional graphene characterizations, process flow of device fabrication, and electron tunneling through the Al/AlO<sub>x</sub>/graphene junction are given in Figures S1–S8. Mobility comparison with other reported flexible FETs is given in Table S1. This material is available free of charge *via* the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- Gelinck, G. H.; Huitema, H. E.; van Veenendaal, E.; Cantatore, E.; Schrijnemarkers, L.; van der Putten, J. B. P. H.; Geuns, T. C. T.; Beenhakkers, M.; Giesbers, J. B.; Huisman, B. H.; et al. Flexible Active-Matrix Displays and Shift Registers Based on Solution-Processed Organic Transistors. Nat. Mater. 2004, 3, 106–110.

- Zhou, L.; Wanga, A.; Wu, S. C.; Sun, J.; Park, S.; Jackson, T. N. All-Organic Active Matrix Flexible Display. *Appl. Phys. Lett.* 2006, *88*, 083502.

- Sekitani, T.; Noguchi, Y.; Hata, K.; Fukushima, T.; Aida, T.; Someya, T. A Rubberlike Stretchable Active Matrix Using Elastic Conductors. *Science* 2008, *321*, 1468–1472.

- Gelinck, G.; Heremans, P.; Nomoto, K.; Authopoulos, T. D. Organic Transistors in Optical Displays and Microelectronic Applications. *Adv. Mater.* **2010**, *22*, 3778–3798.

- Sekitani, T.; Zschieschang, U.; Klauk, H.; Someya, T. Flexible Organic Transistors and Circuits with Extreme Bending Stability. *Nat. Mater.* 2010, *9*, 1005–1022.

- Mannsfeld, S. C. B.; Tee, B. C. K.; Stoltenberg, R.; Chen, C. V. H. H.; Barmann, S.; Muir, B. V. O.; Sokolov, A. N.; Reese, C.; Bao, Z. Highly Sensitive Flexible Pressure Sensors with Microstructured Rubber Dielectric Layers. *Nat. Mater.* 2010, *9*, 859–864.

- Baude, P. F.; Endur, D. A.; Haase, M. A.; Kelley, T. W.; Muryres, D. V.; Theiss, S. D. Pentacene-Based Radio-Frequency Identification Circuitry. *Appl. Phys. Lett.* **2003**, *82*, 3964.

- Klauk, H.; Zschieschang, U.; Pflaum, J.; Halik, M. Ultralow-Power Organic Complementary Circuits. *Nature* 2007, 445, 745–748.

- Yan, H.; Zheng, Y.; Blache, R.; Newman, C.; Lu, S.; Woerle, J.; Facchetti, A. Solution Processed Top-Gate *n*-Channel Transistors and Complementary Circuits on Plastics Operating in Ambient Conditions. *Adv. Mater.* **2008**, *20*, 3393–3398.

- Chen, J. H.; Ishigmi, M.; Jang, C.; Hines, D.; Fuher, M. S.; Williams, E. D. Printed Graphene Circuits. *Adv. Mater.* 2007, *19*, 3623–3627.

- Kim, B. J.; Jang, H.; Lee, S.-K.; Hong, B. H.; Ahn, J.-H.; Cho, J. H. High-Performance Flexible Graphene Field Effect Transistors with Ion Gel Gate Dielectrics. *Nano Lett.* **2010**, *10*, 3464–3466.

- Farmer, D. B.; Lin, Y. M.; Avouris, Ph. Graphene Field-Effect Transistors with Self-Aligned Gates. *Appl. Phys. Lett.* 2010, *97*, 013103.

- Lin, Y. C.; Jin, C.; Lee, J. C.; Jen, S.-F.; Suenaga, K.; Chiu, P. W. Clean Transfer of Graphene for Isolation and Suspension. *ACS Nano* 2011, *5*, 2362–2368.

- Lin, Y. C.; Lu, C. C.; Yeh, C. H.; Jin, C.; Suenaga, K.; Chiu, P. W. Graphene Annealing: How Clean Can It Be?. *Nano Lett.* **2012**, *12*, 414–419.

- Lin, Y. M.; Dimitrakopoulos, C.; Jenkins, K. A.; Farmer, D. B.; Chiu, H. Y.; Grill, A.; Avouris, Ph. 100-GHz Transistors from Wafer-Scale Epitaxial Graphene. *Science* **2010**, *327*, 662.

- Lin, Y. M.; Jenkins, K. A.; Valdes-Garcia, A.; Small, J. P.; Farmer, D. B.; Avouris, Ph. Operation of Graphene Transistors at Gigahertz Frequencies. *Nano Lett.* 2009, *9*, 422–426.

- Liao, L.; Bai, J.; Lin, Y. C.; Qu, Y.; Huang, Y.; Duan, X. High-Performance Top-Gated Graphene-Nanoribbon Transistors Using Zirconium Oxide Nanowires as High-Dielectric-Constant Gate Dielectrics. *Adv. Mater.* **2010**, *22*, 1–5.

- Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Piner, R.; Velamakanni, A.; Jung, I.; Tutuc, E.; *et al.* Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils. *Science* **2009**, *324*, 1312–1314.

- Li, S. L.; Miyazki, H.; Kumatani, A.; Kanda, A.; Tsukagoshi, K. Low Operating Bias and Matched Input–Output Characteristics in Graphene Logic Inverters. *Nano Lett.* **2010**, *10*, 2357–2362.

- Li, S. L.; Miyazki, H.; Hiura, H.; Liu, C.; Tsukagoshi, K. Enhanced Logic Performance with Semiconducting Bilayer Graphene Channels. ACS Nano 2011, 5, 500–506.

- Zschieschang, U.; Ante, F.; Schörholz, M.; Schmidt, M.; Kern, K.; Klauk, K. Mixed Self-Assembled Monolayer Gate Dielectrics for Continuous Threshold Voltage Control in Organic Transistors and Circuits. *Adv. Mater.* **2010**, *22*, 4489–4493.

- Jedaa, A.; Burkhardt, M.; Zschieschang, U.; Klauk, K.; Habich, D.; Schmid, G.; Halik, M. The Impact of Self-Assembled Monolayer Thickness in Hybrid Gate Dielectrics for Organic Thin-Film Transistors. *Org. Electron.* 2009, 10, 1442–1447.

- 23. Gloos, K.; Koppinen, P. J.; Pekola, J. P. Properties of Native Ultrathin Aluminium Oxide Tunnel Barriers. J. Phys.: Condens. Matter **2003**, *15*, 1733–1746.

- Giovannetti, G.; Khomyakov, P. A.; Brocks, G.; Karpan, V. M.; van den Brink, J.; Kelly, P. J. Doping Graphene with Metal Contacts. *Phys. Rev. Lett.* **2008**, *101*, 026803.

- McCreary, K. M.; Pi, K.; Kawakami, R. K. Metallic and Insulating Adsorbates on Graphene. *Appl. Phys. Lett.* 2011, 98, 192101.

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. Realization of a High Mobility Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. *Appl. Phys. Lett.* **2009**, *94*, 062107.

- Miyazaki, H.; Li, S.; Kanda, A.; Tsukagoshi, K. Resistance Modulation of Multilayer Graphene Controlled by the Gate Electric Field. *Semicond. Sci. Technol.* **2010**, *25*, 1–8.

- Bunker, B. C.; Nelson, G. C.; Zavadil, K. R.; Barbour, J. C.; Wall, F. D.; Sullivan, J. P.; Windisch, C. F.; Engelhardt, M. H.; Baer, D. R. Hydration of Passive Oxide Films on Aluminum. *J. Phys. Chem. B* 2002, *106*, 4705–4713.

- Rippard, W. H.; Perrella, A. C.; Albert, F. J.; Byharman, R. A. Ultrathin Aluminum Oxide Tunnel Barriers. *Phys. Rev. Lett.* 2002, *88*, 046805.

- Jennsion, D. R.; Schultz, P. A.; Sullivan, J. P. Evidence for Interstitial Hydrogen as the Dominant Electronic Defect in Nanometer Alumina Films. *Phys. Rev. B* 2004, 69, 041405.